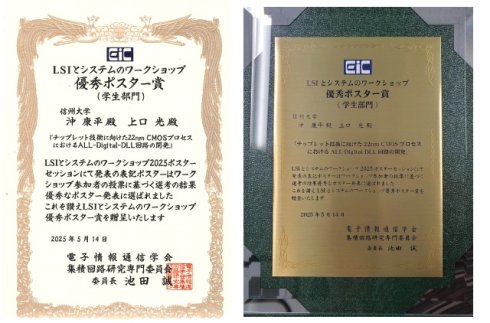

沖康平さんがLSIとシステムのワークショップ2025において優秀ポスター賞(学生部門)を受賞

2025年5月13日、14日に東京都文京区で開催されたLSIとシステムのワークショップ2025のポスター発表において、大学院総合理工学研究科沖康平さん(上口研究室)が、LSIとシステムのワークショップ優秀ポスター賞(学生部門)を受賞しました。

発表内容は以下のとおりです。

チップレット実装技術への応用を目的として、22nm CMOSプロセスを用いて、ALL-Digital DLL回路を開発した。8GT/sのUCIe標準規格に対応する入出力回路において、サンプリングや出力信号の位相調整に必要なグローバルクロックと同期した信号と、それに対し90°ずつの位相差を持つ信号生成を実現するため、Delay-Lock-Loop(DLL)回路およびDuty-Cycle-Correction(DCC)回路を設計した。本回路は低消費電力・小面積・高い移植性を見込み、スタンダードセルのみを用いてALL Digitalでの構成とし、遅延制御には単位遅延を用いたCoarseとCurrent-Mode-Logicを用いたFineの2段階制御を採用した。提案回路では、高速ロックと高精度な同期を実現し、DCC回路によるDuty比補正を並列に行う。回路設計を行った結果、DLLのスキューは約2.1〜4.1ps、Duty比の誤差は一部条件を除き1周期の2%以内の精度を達成し、スタンダードセルのみを用いた対象の回路の構成が可能であることを示した。

沖康平、上口光(信州大学)

チップレット技術に向けた22nm CMOSプロセスにおけるALL-Digital-DLL回路の開発

https://www.gakkai-web.net/ieice/icd/doc/LSI-WS_Poster_Program_rev3.pdf